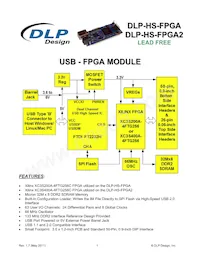

DLP-HS-FPGA2 데이터 시트

|

제조업체 DLP Design Inc. 시리즈 FPGA 모듈 / 보드 유형 FPGA, USB Core 코어 프로세서 Spartan-3A, XC3S400A 공동 프로세서 FT2232H 속도 66MHz 플래시 크기 - RAM 크기 32MB 커넥터 유형 USB - B, Pin Header 크기 / 치수 3" x 1.2" (76.2mm x 30.5mm) 작동 온도 - |